leehyeon-dv 님의 블로그

4.6 Pipelined Datapath and Control 본문

🔑Table of Contents

- MIPS Pipelined Datapath

- Pipeline registers

- Pipeline Operation

- IF for Load, Store ...

- ID for Load, Store ...

- EX for Load, Store ...

- MEM for Load, Store

- WB for Load,Store

- Corected Datapath for Load

- Multi-Cycle Pipeline Diagram

- Multi-Cycle Pipleline Diagram

- Single-Cycle Pipeline Diagram

- Pipelined Control (Simplified)

- Pipelined Control

- Pipelined Control

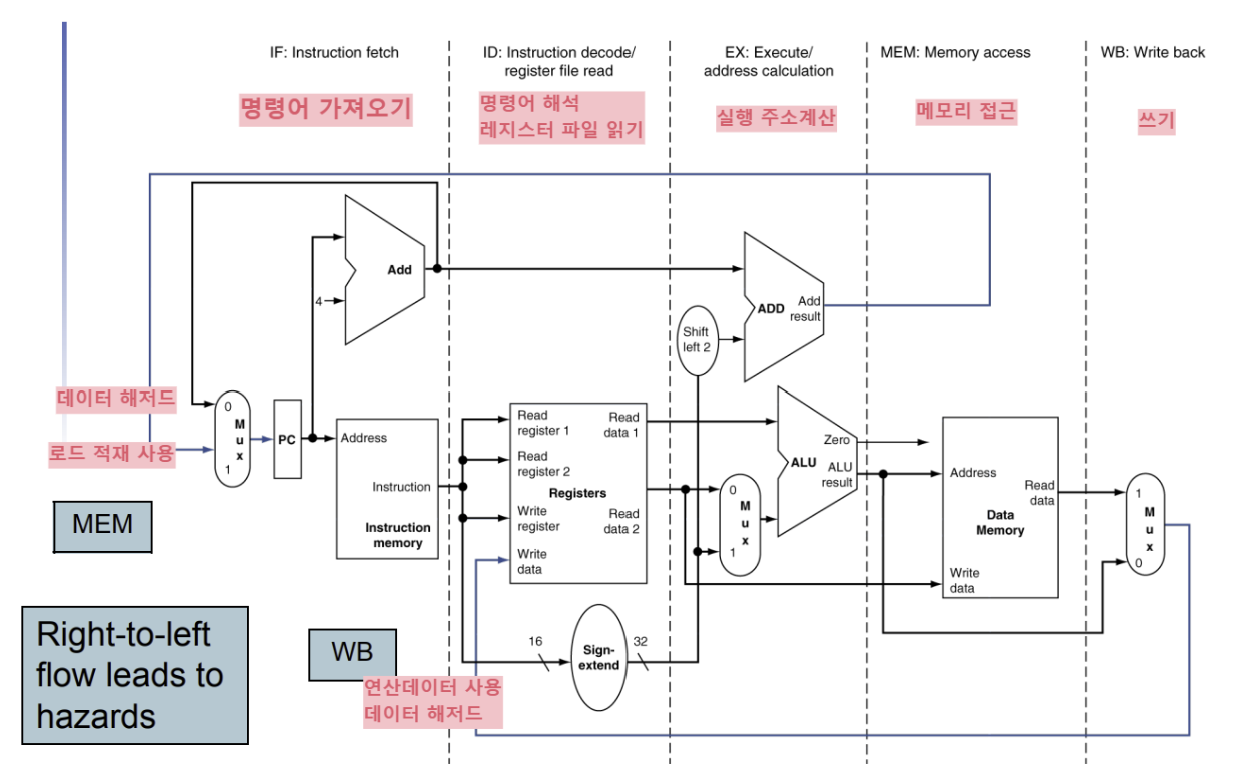

📌 MIPS Pipelined Datapath

- IF(명령어 인출)

- 제어 해저드 :분기명령어로 잘못된 명령어 가져올 위험 있음

- ID (명령어 해석,레지스터파일 읽기)

- 데이터 해저드 : 이전 명령어의 결과가 아직 레지스터에 쓰여지지 않았을 경우 값이 준비되지 않을위험

- EX (실행/주소 계산)

- 데이터 해저드

- MEM (메모리 접근)

- 계산된 주소를 사용해 데이터 메모리값을 읽거나 씀(lw, sw)

- 데이터 해저드

- WB (쓰기)

- 데이터해저드

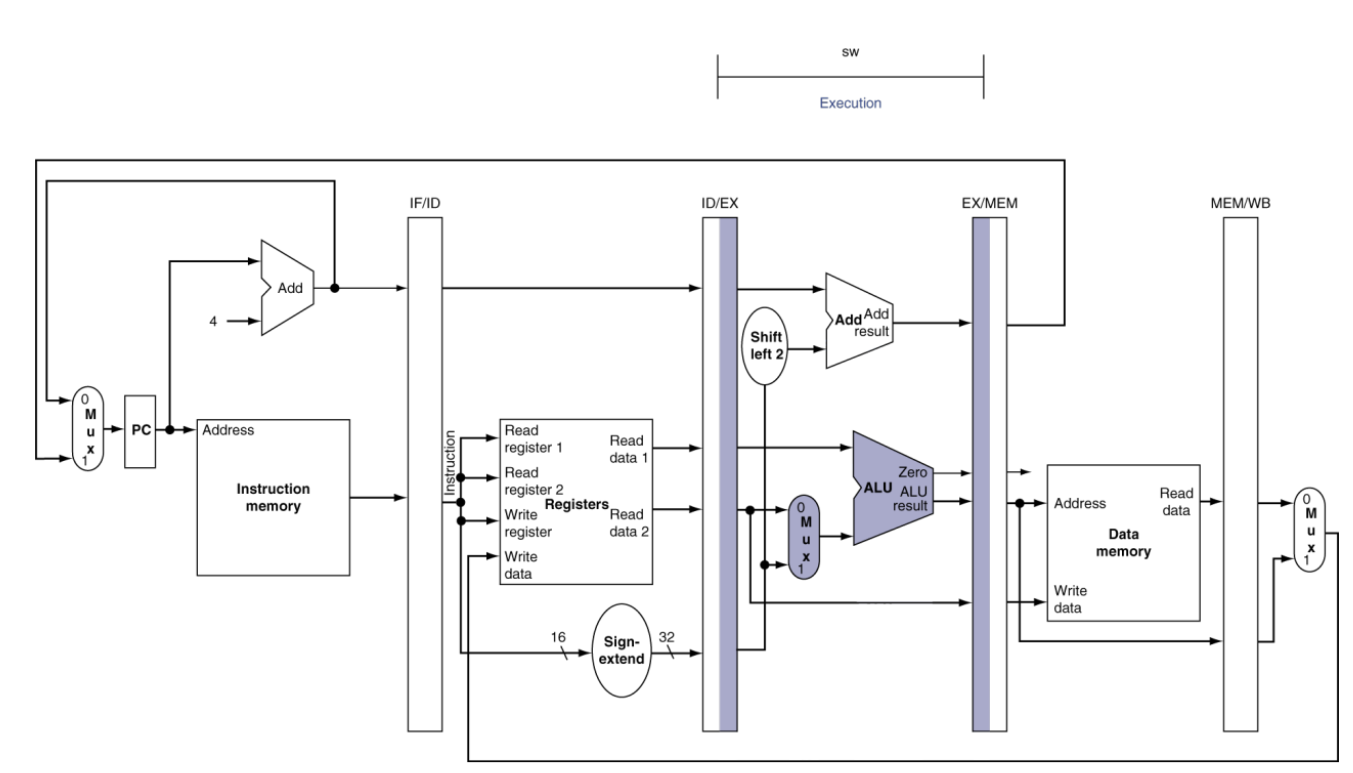

📌 Pipeline registers

각 stage사이에 레지스터들이 필요하다(레지스터수 = stage수-1)

→ 이전 사이클에서 만들어진 정보를 가지고 있어야하기 때문에

lw / sw

lw

sw

R-format

📌 Pipeline Operation

각 명령어가 pipeline datapath의 여러단계를 거쳐 동시에 처리되는 방식

📌IF for Load, Store ...

색 = 사용되고 있는 부분 ( 왼: 쓰기, 오: 읽기)

- 동작 : 현재 pc값에 따라 명령어 메모리에서 명령어를 읽어옴

- 다음 명령어 주소를 계산하기 위해 PC +4 연산

- 분기나 점프가 없으면 PC + 4 값이 다음 명령어 주소가 됨

📌ID for Load, Store ...

- 동작 : 명령어 해석해 필요한 레지스터 값을 읽음

- i값 부호확장

- 명령어 연산되는 두 레지스터 값 읽음

📌EX for Load, Store ...

(Load)

- 동작 : ALU를 사용해 명령어에 필요한 연산 수행

- :Load/Store 명령어의 경우 : rs + offset계산

- :일반 명령어의 경우 두 레지스터 값 계산

(Store)

📌MEM for Load, Store

(Load)

- 동작 : lw(주소를 사용해 데이터 메모리에서 데이터를 읽음)

- sw(주소를 사용해 데이터 메모리에서 데이터를 씀)

(Store)

📌WB for Load,Store

(Load)

- 동작 : lw(읽어온 데이터를 지정된 레지스터에 기록)

- 산술연산 명령어(ALU결과를 레지스터에 기록)

(Store)

store명령어는 데이터 저장작업을 MEM단계에서 완료한

📌Corected Datapath for Load

파이프라인 구조에서는 명령어가 실행될때

각 스테이지가 독립적으로 동작하기때문에 ,

$rt와 같은 명령어 데이터를 다음 스테이지로 전달해야한다

- 이렇게 함으로써 WB에서 다시 레지스터에 전달하여 활용

📌 Multi-Cycle Pipeline Diagram

시간과 명령어에 따른 resource(하드웨어 자원)의 사용(어떤 부분이 사용되는지 보기)

산술연산명령어 → 메모리에서 데이터를 가져올 필요가

없음

load/Store명령어 → 메모리에 직접 접근해 데이터를 읽거나

쓰는 것이 목적

📌 Multi-Cycle Pipleline Diagram

전통적인 보통의 형태

각 사이클 별로 박스로 표현한 모습

클럭사이클 5번에 모든 명령어가 나와있음

📌 Single-Cycle Pipeline Diagram

주어진 사이클에서 파이프라인의 상태 ( 특정 사이클에서 각 stage들이 어떤 명령어를 수행하고 있는지)

위의 그림에서 사이클 5번단계의 모습을 그린거임

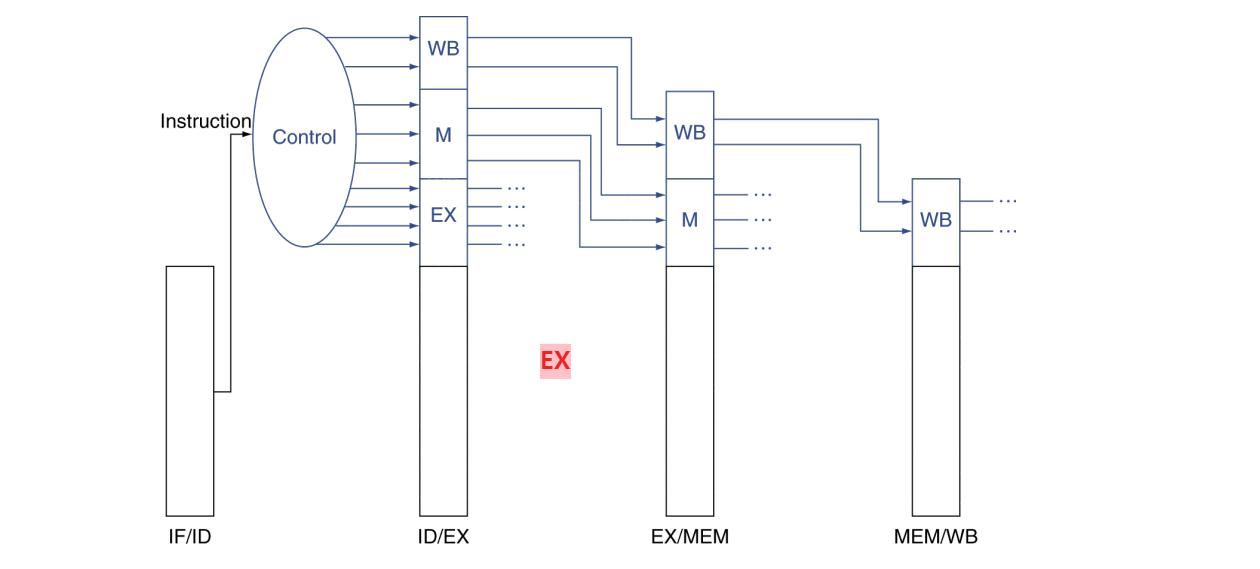

📌 Pipelined Control (Simplified)

간결화된

📌 Pipelined Control

제어신호는 명령어로부터 파생된다 (싱글사이클에서 처럼)

📌Pipelined Control

'컴퓨터구조 및 설계 > 4장. The Processor' 카테고리의 다른 글

| 4.9 Exceptions (1) | 2024.12.11 |

|---|---|

| 4.8 Control Hazards (0) | 2024.12.11 |

| 4.5 An Overview of Pipelining (0) | 2024.12.11 |

| 4.4 A Simple Implementation Scheme (0) | 2024.12.10 |

| 4.3 Building a Datapath (0) | 2024.11.21 |